Iranian Journal of Electrical and Electronic Engineering

Journal Homepage: ijeee.iust.ac.ir

## A Novel Active Feedback Frequency Compensation Scheme for Two-Stage OTA

H. Faraji Baghtash\*(C.A.) and Kh. Monfaredi\*\*

**Abstract:** A novel active feedback frequency compensation scheme is presented in this work. Based on the proposed technique, an amplifier with two main poles in its frequency bandwidth can be easily compensated by introducing a pole-zero pair in a local feedback. The proposed method is mathematically analyzed and then based on the derived formulations, a design procedure is established. The capability of the proposed technique is examined considering a well-known two-stage amplifier, considering just a trivial modification on its input stage. To gain an analogous and fair insight, the performance of the proposed structure is compared with that is of the optimally designed miller-compensated two-stage amplifier. The post-layout simulations are accomplished with TSMC 180nm CMOS standard technology. The Spectre post-layout simulations show that the proposed structure outperforms the traditional structure in terms of power consumption and gain bandwidth product. The robustness of the design is checked with Monte Carlo simulations.

Keywords: Low Voltage, Low Power, Frequency Compensation, Operational Amplifier.

### 1 Introduction

PERATIONAL trans-conductance amplifier (OTA), is essentially one of the most common and widely used blocks in analog signal processing [1-4]. Beside its vast usage in application requiring signal amplification, they have been also known as versatile blocks, finding widespread applications in many structures such as voltage followers, current-to-voltage convertors, active rectifiers, integrators, and various types of filters. Among other specifications of the OTA blocks, the DC-gain and operating frequency bandwidth are considered as the two most important parameters that normally required to be maximized during the design procedure. Unfortunately, there is a severe tradeoff between these two parameters, which means that improving one of these parameters will strictly

E-mail: khmonfaredi@azaruniv.ac.ir.

degrade the other one. Cascoding and cascading of the amplifier blocks are two most common approaches for boosting the overall gain. Due to the supply voltage scaling imposed by nowadays technology downscaling, the performance improvement expected by cascoding is essentially diminished, while the cascading gains more attention than ever. Unfortunately, cascading degrades the stability of the overall amplifier. Hence, the two cascaded stages are typically preferred to maintain the desirable stability. Even with two cascaded stages, the overall amplifier is usually prone to be unstable when used in feedback configurations. Hence the frequency compensation is usually required for two stage OTAs.

JOURNAL OF ELECTRICAL & ELECTRICAL &

So far, several frequency compensation techniques have been proposed for two-stage amplifiers, all of which are variants of well-known Miller compensation scheme [5]. In this scheme, a Miller capacitance is usually inserted between input and output nodes of the second stage (gain stage) [6-9]. This moves the poles of amplifier in opposite directions along the frequency axis, and hence by decreasing the frequency of dominant pole and increasing the frequency of nondominant pole, improves the amplifier stability. The pure Miller compensation technique, however, produces a right half-plane zero. Different variants of Miller compensation scheme have somehow tried to either

Iranian Journal of Electrical and Electronic Engineering, 2019.

Paper first received 07 January 2019 and accepted 27 February 2019. \* The author is with the Faculty of Electrical Engineering, Sahand University of Technology, Tabriz, Iran.

E-mail: hfaraji@sut.ac.ir.

<sup>\*\*</sup> The author is with the Faculty of Engineering, Azarbaijan Shahid Madani University, Tabriz, Iran.

Corresponding Author: H. Faraji Baghtash.

eliminate this right half-plane zero or to turn it to a left half-plane one. For instance, a nulling resistor added in series with the compensation capacitor, makes it possible to effectively remove the right half-plane zero or turn it to a left half-plane zero [10, 11]. Some other variants of Miller compensation have been proposed which exploit voltage follower [12-14], current follower [12, 13, 15, 16], current amplifier [15], or current mirror [17, 18] in feedback or feedforward path.

The miller scheme is indeed proved to be a very effective compensation technique. Although the theory and design procedure of the miller compensation technique are well-established, and hence can be easily used to compensate any two-stage amplifier, but, it has some disadvantages as well. For instance, the miller capacitor degrades the slew rate and destroys the PSRR of the amplifier.

In this work a novel active feedback frequency compensation scheme is presented for two-stage OTAs. The proposed scheme is an alternative method to the conventional miller compensation technique, which effectively overcomes its PSRR degradation problem. The proposed approach requires a much smaller capacitor; leading to a less occupied chip area and adds no extra power to the original amplifier.

The paper is organized as follows. Section 2 describes the concept of the proposed technique. The principal of operation and related mathematical formulations are provided in this section. The simulation results are given in Section 3 and finally, section 4 concludes the paper.

#### 2 The Proposed Compensation Scheme

An appropriately designed two-stage uncompensated amplifier normally has two separate poles with no zeros in its frequency bandwidth. Therefore, the simplified sdomain frequency transfer function of a two-stage amplifier can be given by:

$$A(s) = \frac{A_0}{\left(1 + \frac{s}{p_1}\right)\left(1 + \frac{s}{p_2}\right)} = \frac{A_0 p_1 p_2}{(p_1 + s)(p_2 + s)}$$

(1)

where,  $A_0$ ,  $p_1$ , and  $p_2$  are DC gain, first, and second poles of the amplifier, respectively. Since the amplifier is not frequency compensated, both  $p_1$  and  $p_2$  are smaller than unity-gain bandwidth (GBW), i.e.  $p_1 < p_2 < \text{GBW}$ .

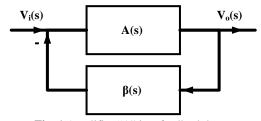

To explain the frequency compensation scheme, let us put the amplifier, A(s), in a feedback loop, as in Fig. 1, and derive some formulas. Doing so, the frequency compensation scheme will be discussed and its effectiveness will be verified as we proceed.

Fig. 1 shows the block diagram of a negative feedback amplifier which is formed by an amplifier "A" and a feedback block " $\beta$ ". The closed-loop transfer function of this feedback system (like that in Fig. 1) is clearly given

Fig. 1 Amplifier "A" in a feedback loop.

by:

$$\frac{V_o}{V_i}(s) = A_{CL}(s) = \frac{A(s)}{1 + A(s)\beta(s)}$$

(2)

The main idea here is to choose the transfer function of  $\beta(s)$  such that the  $A_{CL}(s)$  be frequency compensated. To do so, suppose that  $\beta(s)$  is given by:

$$\beta(s) = \frac{\beta_0 s}{p_f + s} \tag{3}$$

where,  $p_f$  is the pole frequency of  $\beta(s)$  and  $\beta_0$  is a constant coefficient. Substituting A(s) and  $\beta(s)$  from (1) and (3) into (2) gives:

$$A_{CL}(s) = \frac{A_0 p_1 p_2 (p_f + s)}{p_1 p_2 p_f + \lambda s + (p_1 + p_2 + p_f) s^2 + s^3},$$

$$\lambda = p_1 p_2 + p_1 p_f + p_2 p_f + A_0 \beta_0 p_1 p_2$$

(4)

Assuming that  $p_1 < p_2 < p_f < A_0\beta_0p_1$ , Eq. (4) can be simplified to:

$$A_{CL}(s) = \frac{A_0 p_1 p_2 (p_f + s)}{\left(\frac{p_1 p_f}{p_f + A_0 \beta_0 p_1} + s\right) D(s)},$$

$$D(s) = \left(p_f + A_0 \beta_0 p_1\right) p_2 + p_f s + s^2$$

(5)

Examining (5) reveals that the only condition in which  $A_{CL}(s)$  may offer a favorable phase margin (PM) is when D(s) has a  $\Delta < 0$ , i.e. two complex roots. Now, let us evaluate a condition in which the proper phase margin can be achieved. To do so, one may proceed as follows: If we define  $\alpha = p_1 A_0/p_f$ , Eq. (5) can be rewritten as:

$$A_{CL}(s) = \frac{A_0 p_1 p_2 \left(\frac{p_1 A_0}{\alpha} + s\right)}{\left(\frac{p_1}{1 + \alpha \beta_0} + s\right) D(s)},$$

$$D(s) = A_0 \frac{\left(1 + \alpha \beta_0\right)}{\alpha} p_1 p_2 + \frac{p_1 A_0}{\alpha} s + s^2$$

(6)

At unity-gain bandwidth frequency of  $\omega_0 = p_1 A_0 / (1 + \alpha \beta_0)$ , the amplitude of the closed-loop transfer function should be unity, i.e.  $|A_{CL}(\omega_0)| = 1$ .

Considering this condition gives:

$$\left[\frac{1+\alpha\beta_0}{\alpha} - \frac{p_1A_0}{p_2} \cdot \frac{1}{\left(1+\alpha\beta_0\right)^2}\right]^2 + \left[\frac{p_1}{p_2} \cdot \frac{A_0}{\alpha\left(1+\alpha\beta_0\right)}\right]^2 - \left(\frac{1+\alpha\beta_0}{\alpha}\right)^2 = 1$$

(7)

On the other hand, at unity-gain bandwidth frequency, the phase margin requirement should be satisfied as well, i.e.  $PM = \measuredangle A_{CL}(\omega_0) + 180$ . Calculating the *PM* of (6) at  $\omega = \omega_0$  gives:

$$PM = 180 + \tan^{-1}\left(\frac{\omega_0}{p_f}\right) - \tan^{-1}\left(\frac{\omega_0\left(1+\alpha\beta_0\right)}{p_1}\right) - \measuredangle D(s),$$

$$\measuredangle D(s) = \tan^{-1}\left(\frac{\alpha\left(2\omega_0 - \sqrt{|\Delta|}\right)}{p_1A_0}\right) + \tan^{-1}\left(\frac{\alpha\left(2\omega_0 + \sqrt{|\Delta|}\right)}{p_1A_0}\right) \quad (8)$$

where,  $\Delta$  is given by:

$$\Delta = \left(\frac{p_1 A_0}{\alpha}\right)^2 - 4A_0 \frac{\left(1 + \alpha \beta_0\right)}{\alpha} p_1 p_2 \tag{9}$$

Replacing  $\omega_0$  by its equivalence in (8) gives:

$$PM = 90 + \tan^{-1} \left( \frac{\alpha}{1 + \alpha \beta_0} \right) - \measuredangle D(s),$$

$$\measuredangle D(s) = \tan^{-1} \left( \left[ \frac{2\alpha}{1 + \alpha \beta_0} - \sqrt{\frac{4p_2 \alpha (1 + \alpha \beta_0)}{p_1 A_0}} - 1 \right] \right)$$

$$+ \tan^{-1} \left( \left[ \frac{2\alpha}{1 + \alpha \beta_0} + \sqrt{\frac{4p_2 \alpha (1 + \alpha \beta_0)}{p_1 A_0}} - 1 \right] \right)$$

(10)

Solving (7) and (10), gives the values of  $\alpha$  and  $\beta_0$  that satisfy the required phase margin. The resulted values are not exact, as some approximations have been considered to derive these equations; however, they give a good start point to initiate some iterations to find the proper values that truly satisfy the phase margin requirements.

In the following section the realization of the proposed compensation scheme on a two stage amplifier is discussed.

# 3 Circuit Realization Based on the Proposed Scheme

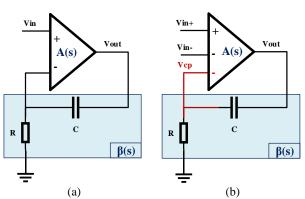

In this section, the proposed compensation method is embedded on a well-known two stage amplifier to examine its performance. Let us initially investigate the effect of the proposed scheme on an ideal two-pole opamp block, before considering the aforementioned two stage amplifier. Fig. 2(a) depicts a realization of the proposed compensation technique where,  $\beta(s)$  is given by  $\beta(s) = s/(s + 1/RC)$ . As can be seen in Fig. 2(a), despite the simple realization of the proposed technique, this configuration imposes a serious limitation on the compensated amplifier. In other words, its negative input is not available anymore when it is utilized in a feedback loop. To resolve this issue, the amplifier structure requires a little modification. This can be simply accomplished by adding an extra inverting input to the amplifier considering, as is shown in Fig. 2(b). Considering this inverting input, the amplifier has two distinct inverting ports, one is used for the realization of the compensation network and the other one is available for any other application, such as general feedback network configuration. Undoubtedly, this is not the only application that the proposed scheme can be applied to, and other configurations compatible with the proposed compensation technique can be certainly found or developed. Nevertheless, this article aims to show the performance of the proposed compensation scheme in a simple configuration.

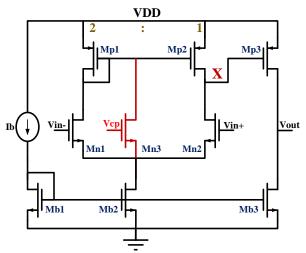

Fortunately, the realization of the modified 3-input amplifier is very straightforward. Fig. 3 depicts the transistor level implementation of the modified amplifier. As it can be seen in Fig. 3, the third input is obtained simply by embedding an extra NMOS transistor satisfying the DMOS design methodology conditions [19], highlighted with red color, in the differential pair of amplifier.

Now, let us derive some formulations for expressing some of the small-signal characteristics of the proposed amplifier shown in Fig. 3.

#### 3.1 The Frequency Response Analysis

Considering the resistances seen from the drains of Mp2 and Mp3, respectively as R<sub>1</sub> and R<sub>11</sub>, and regarding that  $g_{mn1} = g_{mn2} = g_{mn3} = g_1$  and  $g_{mp3} = g_{11}$ , the following equations can be written.

$$V_{out} = -g_{II}R_{II} \left( -g_{I}V_{gs2} + \frac{g_{I}V_{gs1}}{2} + \frac{g_{I}V_{gs3}}{2} \right)R_{I}$$

(11)

**Fig. 2** Realization of the proposed compensation scheme on an ideal two-pole Amplifier, a) the original, and b) the modified version.

Fig. 3 The transistor level realization of the 3-input amplifier.

where,

$$R_{I} = r_{op2} + 1.5r_{on2}, \quad R_{II} = r_{op3} + r_{ob3}$$

(12)

Performing some simplifications gives:

$$V_{out} = g_I g_{II} R_I R_{II} \left( V_{in+} - \frac{V_{in-}}{2} - \frac{V_{cp}}{2} \right)$$

(13)

From (12), it can be observed that if the two negative input ports of the proposed amplifier are tied together, the proposed amplifier acts as a regular amplifier (with two input ports) with differential DC gain of  $A_V(0) = g_I g_{II} R_I R_{II}$ . On the other hand, if the proposed amplifier is configured as Fig. 2(b) with positive input node tied to the ground ( $V_{in+} = 0$ ), the DC voltage gain is given by  $A_V(0) = g_I g_{II} R_I R_{II}/2$ .

Considering  $V_{in+} = 0$  and substituting  $V_{cp} = \beta V_{out}$  into (13) gives:

$$\frac{V_{out}}{V_{in-}} = -\frac{A_0}{1 + A_0\beta}$$

(14)

where,

$$A_0 = \frac{g_I g_{II} R_I R_{II}}{2}$$

(15)

So far, the effects of the parasitic capacitances are neglected in gain analysis, yielding just the DC voltage gain. As it will be shown in the next section (see Fig. 4), the proposed amplifier has two distinct poles in its operating frequency range. Considering Fig. 3, these two poles occur at frequencies equal to  $p_1 = 1/R_I C_I$  and  $p_2 = 1/R_{II} C_{II}$ , where,  $C_I$  and  $C_{II}$  are given by (16), Hence, Eq. (14) can be rewritten as (17)

$$C_{I} = c_{dsp2} + c_{dsn2} + c_{gsp3},$$

$$C_{II} = c_{dsp3} + c_{dsb3} + c_{L}$$

(16)

Fig. 4 The configuration of the proposed amplifier to evaluate the PSRR.

$$\frac{V_{out}}{V_{in-}} = -\frac{A(s)}{1+A(s)\beta(s)}, \quad \beta(s) = \frac{RCs}{1+RCs},$$

$$A(s) = \frac{A_0}{\left(1+\frac{s}{p_1}\right)\left(1+\frac{s}{p_2}\right)}$$

(17)

The Eq. (17) shows that if the proposed amplifier is configured as Fig. 2(b), its frequency transfer function is Analogous with that is of Fig. 1 (refer to (2)). Therefore, the formulations derived in previous section can be exploited to obtain the frequency response of the compensated amplifier, as well as, the corresponding values for R and C that satisfy (10).

#### 3.2 The PSRR Analysis

To evaluate the PSRR of the proposed circuit, consider the amplifier configuration as in Fig. 4, where the power supply variations is shown with  $V_{dd}$ . Respecting this figure, the output voltage can be defined as:

$$V_{out} = -\frac{A(s)}{2} V_{in-} - \frac{A(s)}{2} V_{cp} + A_{dd}(s) V_{dd}$$

(18)

where  $A_{dd}(s)$  is the voltage gain from  $V_{dd}$  to  $V_{out}$ . Replacing  $V_{cp}$  with  $\beta V_{out}$  in (18) gives:

$$V_{out} = -\frac{A(s)}{2 + A(s)\beta(s)}V_{in-} + \frac{2A_{dd}(s)}{2 + A(s)\beta(s)}V_{dd}$$

(19)

Recalling the definition of the PSRR which is given by  $(V_{out}/V_{in})/(V_{out}/V_{dd})$ , from (19), the PSRR of the proposed circuit is given by:

$$\left| PSRR \right| = \frac{A(s)}{2A_{dd}(s)} \tag{20}$$

The A(s) already is defined in (17), though if  $A_{dd}(s)$  can be determined properly, the PSRR can be obtained accordingly. To do so, we need to tie the inputs of the amplifier to the ground and obtain the transfer function from  $V_{dd}$  to  $V_{out}$ . Fortunately, in this configuration, the proposed amplifier acts exactly like a traditional uncompensated two-stage amplifier. Therefore,  $A_{dd}(s)$  is given by [20, 21]:

$$A_{dd}\left(s\right) \approx \frac{1}{1 + \frac{s}{p_1}} \tag{21}$$

Substituting A(s) and  $A_{dd}(s)$  from (17) and (21) in to (20) gives the PSRR value as:

$$\left|PSRR\right| = \frac{A_0}{2\left(1 + \frac{s}{p_2}\right)} \tag{22}$$

#### 4 Post-Layout Simulation Results

The performance of the proposed compensation

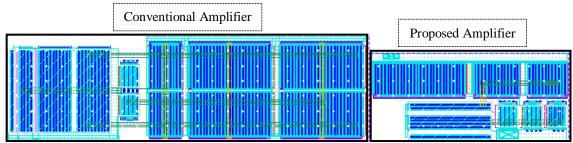

scheme and its application on the modified two-stage amplifier (see Fig. 3) is investigated through Spectre post-layout simulations with TSMC 180nm CMOS standard technology. After compensation, the performance of the proposed structure is compared with that is of the traditional two-stage miller-compensated amplifier. To have a fair comparison, each amplifier is optimally designed and compensated to have 50° phase margin at the presence of a 30pF load capacitance. The layout view of the amplifiers is shown in Fig. 5. The transistors' aspect ratios and the amplifiers' bias conditions are summarized in Table 1.

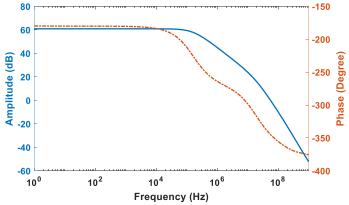

The frequency behavior of an uncompensated twostage amplifier, with the specifications given in Table1, is shown in Fig. 6. This figure shows that the amplifier has two poles in its frequency bandwidth, making the frequency compensation necessary to enable the amplifier to be appropriately used in feedback configurations. The poles are evaluated to be  $p_1 = 162$  kHz and  $p_2 = 18.75$  MHz.

| Device Name | Traditional   | Proposed    |

|-------------|---------------|-------------|

| Ib          | 56 µA         | 100 µA      |

| Mb1         | 27µm/540nm    | 27µm/540nm  |

| Mb2         | 108µm/540nm   | 108µm/540nm |

| Mb3         | 540µm/540nm   | 54µm/540nm  |

| Mn1, Mn2    | 56µm/180nm    | 56µm/180nm  |

| Mn3         | NA            | 56µm/180nm  |

| Mp1         | 140µm/540nm   | 280µm/540nm |

| Mp2         | 140µm/540nm   | 140µm/540nm |

| Mp3         | 2*700µm/540nm | 140µm/540nm |

Table 1 The birs and distance and the maintain? dimensions

Fig. 5 The layout view of the design.

Fig. 6 The frequency behavior of the uncompensated two-stage amplifier.

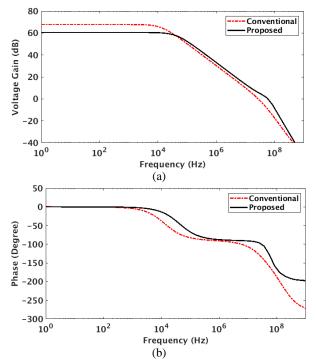

The numerical values of  $\alpha$  and  $\beta_0$  must be obtained to compensate the circuit with the proposed compensation scheme. Considering the configuration of Fig. 2(b), the value of  $\beta_0$  is obtained 0.66. Substituting the values of  $\beta_0$ ,  $p_1$ , and  $p_2$  into (10), gives the value of  $\alpha$  for a specified PM. Taking 50° phase margin into account, the value of  $\alpha$  evaluated to be 2.23. The value of  $\alpha$  equal with 2.23 is translated to the 80MHz pole frequency in the feedback network, i.e.  $p_f = 80MHz$ . This gives the RC value of about 2ns. Selecting the value of  $R = 6k\Omega$ , gives the value of C = 0.33 pF. Simulating the compensated amplifier with the values obtained for R and C, the phase margin of about 47° is obtained which is very close to the desired value. To achieve a strictly precise result, the design is re-simulated by sweeping the value of C around its predicted value. This gives the proper value for C, that is C = 0.4pF, which essentially delivers the required 50° phase margin. As stated in the first paragraph of this section, an optimally designed miller compensated amplifier is considered to compare its performance with that is of the proposed structure. Fig. 7 shows the frequency behavior of the proposed circuit versus frequency behavior of the traditional miller compensated amplifier.

As can be observed from Fig. 7, both of the amplifiers deliver the same amount of PM, which is about 50°. Comparing the results, it is clear that the traditional amplifier presents a little higher DC gain, however, its maximum operating frequency is much less than the proposed one. In other word, the proposed structure delivers a larger gain bandwidth product value, which makes it more suitable for high frequency applications. The power supply rejection ratios (PSRR) of both

amplifiers are compared in Fig. 8. As is shown, although the PSRR value of the proposed structure is less than that is of the traditional one in lower frequencies, but the PSRR of the traditional amplifier starts to roll off much faster, presenting much less PSRR than the proposed amplifier in higher operating frequencies (especially in Fig. 8 (a)). This, in fact, was predictable as it is the intrinsic disadvantage of the miller compensated amplifiers. The higher DC value of PSRR in traditional amplifier is due to its higher DC gain in this specific design.

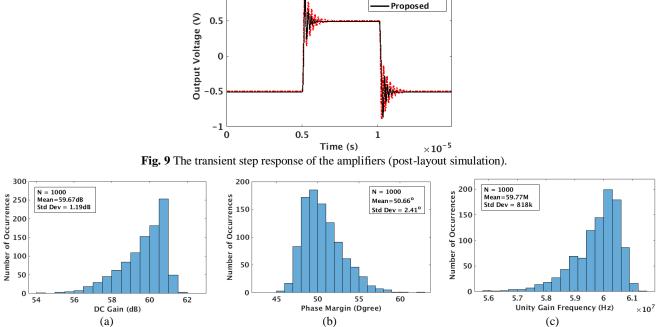

The transient step response of the proposed amplifier is compared with the response of traditional amplifier in Fig. 9. As this figure shows, both of the amplifiers are stable and deliver fast rising and settling time. As is shown in Fig. 9, the proposed structure settles two times faster than the traditional amplifier.

To evaluate the robustness of the proposed structure against process uncertainties, the Monte Carlo simulation is performed to examine the two most important and vulnerable parameters, namely phase margin and DC gain. As is shown in the histograms of Fig. 10, the robustness of the proposed structure is acceptable, which assures its well-functionality after fabrication.

The important specifications of the proposed structure, incorporating the novel active feedback compensation scheme is compared with that is of the traditional miller compensated amplifier in Table 2. Examining Table 2 shows that the two amplifiers are almost the same in most of the parameters except the merits of gain bandwidth product and power consumption. In fact, the amplifier designed based on the proposed compensation

**Fig. 7** The frequency behavior of the compensated amplifiers, a) amplitude, and b) phase (post-layout simulation).

Fig. 8 The PSRR performance of the amplifiers, a) PSRR+, and b) PSRR- (post-layout simulation).

1

Conventiona

Fig. 10 The Monte Carlo analysis of the proposed amplifier, a) the DC gain, b) the phase margin, and c) the unity gain frequency (postlayout simulation).

| Table 2 The spe | cifications of the prop | osed amplifier versus | s those of the traditional scheme. |

|-----------------|-------------------------|-----------------------|------------------------------------|

|-----------------|-------------------------|-----------------------|------------------------------------|

| Deremeters             | Pre-Layout Simulation |          | Post-Layout Simulation |          |

|------------------------|-----------------------|----------|------------------------|----------|

| Parameters             | Traditional           | Proposed | Traditional            | Proposed |

| VDD (V)                | 1.8                   | 1.8      | 1.8                    | 1.8      |

| Power (mW)             | 2.588                 | 1.255    | 2.46                   | 1.06     |

| PSRR+(dB)              | 72.7                  | 59.1     | 72.6                   | 56.9     |

| PSRR- (dB)             | 83.7                  | 70       | 66.6                   | 70.38    |

| Slew Rate (v/µs)       | 13.8                  | 11.1     | 13.4                   | 10.5     |

| 10% Settling Time (µs) | 1                     | 0.5      | 1.1                    | 0.6      |

| Gain (dB)              | 67                    | 60       | 67.8                   | 60.52    |

| Phase Margin           | 51.1                  | 50.8     | 49.45                  | 49.54    |

| Gain Bandwidth (MHz)   | 29.3                  | 61.5     | 28.44                  | 60.58    |

| Load Capacitance (pF)  | 30                    | 30       | 30                     | 30       |

scheme delivers much more gain bandwidth product consuming much less power. This makes the proposed structure more power efficient and favorable for low power and high speed applications.

### 5 Conclusion

A novel active feedback frequency compensation scheme is presented in this work. The Spectre post layout simulations proved that a two-stage amplifier can be well-compensated based on the proposed active feedback frequency compensation scheme. The effectiveness of the proposed method is also verified through the mathematical formulations as well. The simulations were done utilizing TSMC 180nm CMOS standard technology. The Spectre post layout simulations showed that the proposed structure outperforms the traditional structure in terms of power consumption and gain bandwidth product. The robustness of the design was checked with Monte Carlo simulations exhibiting acceptable results.

#### References

- [1] M. Farsi and K. Monfaredi, "A low voltage recycling folded cascode OTA based on novel CMRR magnifier," *Journal of Telecommunication*, *Electronic and Computer Engineering (JTEC)*, Vol. 10, No. 4, pp. 37–42, 2018.

- [2] H. F. Baghtash, K. Monfaredi, and A. Ayatollahi, "A novel±0.5 V, high current drive, and rail to rail current operational amplifier," *Analog Integrated Circuits and Signal Processing*, Vol. 70, No. 1, pp. 103–112, 2012.

- [3] H. F. Baghtash and A. Ayatollahi, "A zero-pole reposition based, 0.95-mW, 68-dB, linear-in-dB, constant-bandwidth variable gain amplifier," *Circuits, Systems, and Signal Processing*, Vol. 33, No. 5, pp. 1353–1368, 2014.

- [4] H. F. Baghtash, "A 0.74 mW, linear-in-dB, constant bandwidth, variable gain amplifier based on zeropole repositioning technique," *Analog Integrated Circuits and Signal Processing*, Vol. 84, No. 2, pp. 303-313, 2015.

- [5] I. Chaharmahali, S. Asadi, B. Dorostkar, M. M. Bosra, and M. Abedini, "A new method modifying single Miller feedforward frequency compensation to drive large capacitive loads: putting an attenuator in the path," *Analog Integrated Circuits and Signal Processing*, Vol. 93, No. 1, pp. 61–70, 2017.

- [6] R. J. Widlar, "Monolithic OP AMP with simplified frequency compensation (Monolithic operational amplifiers with simplified frequency-compensated network using minimum stages and integrated circuit components)," *EEE-The Magazine of Circuit Design Engineering*, Vol. 15, pp. 58–63, 1967.

- [7] G. Palumbo and S. Pennisi, *Feedback amplifiers:* theory and design. Springer Science & Business Media, 2002.

- [8] M. Zaidi, I. Grout, and A. K. A. Ain, "Evaluation of compensation techniques for CMOS operational amplifier design," in *International Conference on IC Design & Technology (ICICDT)*, pp. 5–8, 2018.

- [9] R. A. Sarode and S. S. Chopade, "Design and simulation of two stage operational amplifier with miller compensation in nano regime," in *Proceedings of the International Conference on Data Engineering and Communication Technology*, Singapore, pp. 159–168, 2017.

- [10]G. Palmisano and G. Palumbo, "An optimized compensation strategy for two-stage CMOS op amps," *IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications*, Vol. 42, No. 3, pp. 178–182, 1995.

- [11]H. Aminzadeh and M. Banihashemi, "Miller compensation: optimal design for operational amplifiers with a required settling time," *Circuits, Systems, and Signal Processing*, Vol. 33, No. 9, pp. 2675–2694, 2014.

- [12] M. Tan and Q. Zhou, "A two-stage amplifier with active miller compensation," in *IEEE International Conference on Anti-Counterfeiting, Security and Identification (ASID)*, pp. 201–204, 2011.

- [13]S. H. Pakala, M. Manda, P. R. Surkanti, A. Garimella, and P. M. Furth, "Voltage buffer compensation using flipped voltage follower in a two-stage CMOS op-amp," in *IEEE 58th International Midwest Symposium on Circuits and Systems (MWSCAS)*, pp. 1–4, 2015.

- [14] Y. P. Tsividis and P. R. Gray, "An integrated NMOS operational amplifier with internal compensation," *IEEE Journal of Solid-State Circuits*, Vol. 11, pp. 748–753, 1976.

- [15] W. Aloisi, G. Palumbo, and S. Pennisi, "Design methodology of Miller frequency compensation with current buffer/amplifier," *IET circuits, devices & systems*, Vol. 2, No. 2, pp. 227–233, 2008.

- [16]G. Palmisano and G. Palumbo, "A compensation strategy for two-stage CMOS opamps based on current buffer," *IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications*, Vol. 44, No. 3, pp. 257–262, 1997.

- [17] P. J. Hurst, S. H. Lewis, J. P. Keane, F. Aram, and K. C. Dyer, "Miller compensation using current buffers in fully differential CMOS two-stage operational amplifiers," *IEEE Transactions on Circuits and Systems I: Regular Papers*, Vol. 51, No. 2, pp. 275–285, 2004.

- [18] M. Tan and W. H. Ki, "Current-mirror miller compensation: An improved frequency compensation technique for two-stage amplifiers," in *International Symposium on VLSI Design*, *Automation, and Test (VLSI-DAT)*, pp. 1–4, 2013.

- [19]K. Monfaredi, "Distributed unique-size MOS technique: A promising universal approach capable of resolving circuit design bottlenecks of modern era," *Circuits, Systems, and Signal Processing,* Vol. 38, No. 2, pp. 512–528, 2019.

- [20] P. E. Allen and D. R. Holberg, *CMOS analog circuit design*. Oxford University Press, 2002.

- [21]B. Razavi, *Design of Analog CMOS Integrated Circuits*. McGraw-Hill Education, 2016.

**H. Faraji Baghtash** was born in Miandoab, Iran, in 1985. He received the B.Sc. degree from Urmia University in 2007, and M.Sc. and Ph.D. degrees both from Iran University of Science and Technology (IUST), Tehran, Iran in 2009, and 2014 in respectively, all in Electronics Engineering. He was with IUST Electronic Research Center Group,

from 2007 to 2010 as a Researcher, and Science and Research Branch, Islamic Azad University from 2011 to 2015, as a Fellow Lecturer. He joined Sahand University of Technology, Tabriz, Iran as an Assistant Professor in 2015. He is the author or coauthor of more than 30 national and international papers and also collaborated in several research projects and has a registered Iranian patent. Dr. Faraji Baghtash was selected as distinguished researcher of the IUST in 2011. His current research interests include current mode/voltage mode analog integrated circuit design, low voltage, low power circuit and systems, analog microelectronics and digital system design.

**Kh. Monfaredi** received the B.Sc., M.Sc., and Ph.D. degrees from Tabriz University in 2001 and Iran University of Science and Technology (IUST) in 2003 and 2011, respectively. He was with Electronic Research Center Group, during 2001 to 2011 and was also an academic staff with Islamic Azad University, Miandoab Branch from 2006 to 2012. He

served as the Research and Educational Assistant of Miandoab Sama College from 2009 to 2011 and vice chancellor during 2011 to 2012. He is currently with Electrical and Electronics Engineering Faculty, Azarbaijan Shahid Madani University, Tabriz, Iran. He is the associate dean of engineering faculty, Azarbaijan Shahid Madani University since 2017. He is the author or coauthor of more than thirty national and international papers and also collaborated in several research projects. He is also the founder of electronic department in Islamic Azad University-Miyandoab Branch and was the chairman of 2010 electronic and computer scientific conference (ECSC2010) held in Islamic Azad University, Miandoab Branch. His current research interests include current mode integrated circuit design, low voltage, low power circuit and systems and analog microelectronics and data converters.

© 2019 by the authors. Licensee IUST, Tehran, Iran. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution-NonCommercial 4.0 International (CC BY-NC 4.0) license (<u>https://creativecommons.org/licenses/by-nc/4.0/</u>).